# A PVT-compensated 2.2 to 3.0 GHz Digitally Controlled Oscillator for All-Digital PLL

Anil Kavala, Woorham Bae, Sungwoo Kim, Gi-Moon Hong, Hankyu Chi, Suhwan Kim, and Deog-Kyoon Jeong

Abstract—We describe a digitally controlled oscillator (DCO) which compensates the frequency variations for process, voltage, and temperature (PVT) variations with an accuracy of ±2.6% at 2.5 GHz. The DCO includes an 8 phase current-controlled ring oscillator, a digitally controlled current source process and temperature (PT)counteracting voltage regulator, and a bias current generator. The DCO operates at a center frequency of 2.5 GHz with a wide tuning range of 2.2 GHz to 3.0 GHz. At 2.8 GHz, the DCO achieves a phase noise of -112 dBc/Hz at 10 MHz offset. When it is implemented in an all-digital phase-locked loop (ADPLL), the ADPLL exhibits an RMS jitter of 8.9 ps and a peak to peak jitter of 77.5 ps. The proposed DCO and ADPLL are fabricated in 65 nm CMOS technology with supply voltages of 2.5 V and 1.0 V, respectively.

Index Terms—Digitally controlled oscillator, ring oscillator, PVT compensated DCO, PT-counteracting voltage regulator, all-digital phase-locked loop

#### I. Introduction

The ring-type DCO is perhaps the most widely used element in mixed-signal applications over its LC-type counterpart, with the advantages of generating a

Manuscript received May. 13, 2014; accepted Jun. 5, 2014 The authors are with the Inter-University Semiconductor Research Center (ISRC) and the School of Electrical and Computer Engineering, Seoul National University, Gwanak-ro 599, Gwanak-gu, Seoul, Korea (151-744). E-mail: dkjeong@snu.ac.kr multiphase clock with a wide frequency tuning range in a small area. Apart from its advantages, its frequency is quite sensitive to process, voltage, and temperature (PVT) variations, which limits its use in many applications. In order to ensure correct locking across all these frequency variations in all-digital phase-locked loops (ADPLLs) [1, 2], the DCOs are designed with an extremely wide tuning range which leads to decrease in DCO frequency resolution. This decrease in resolution causes high quantization noise, which is one of the main noise sources of an ADPLL. Also, the loop stability and bandwidth of the ADPLL are strongly dependent on the DCO gain which varies widely due to PVT variations. Therefore, a PVT-tolerant DCO with high frequency resolution is essential to achieve better performance.

The ring-type DCOs with a digitally controlled resistor (DCR) were proposed for high-frequency resolution applications with a wide frequency tuning range [3, 4]. However, their phase noise deteriorates at low supply voltages, due to the voltage drop in their DCR in the main current path of the oscillation. Also, the DCR implemented with on-chip resistors is quite sensitive to PVT variations, which results in a wide DCO resolution variation.

A lot of effort has already been put into overcoming the oscillator frequency PVT variations. The recent oscillator designs [5, 6, 9] which were aimed at compensating these variations while saving area without using bandgap reference (BGR) or regulator are able to compensate partially across all PVT variations. In the design of 130-MHz ring oscillator [5], the effect of PVT variations is reduced by a temperature and process compensation circuit and a replica feedback bias circuit.

This achieved a frequency variation of  $\pm 11.52\%$  across all PVT corners. A compensation technique shown in [6] uses an addition-based current source to supply the bias current to the oscillator. But this design does not offer supply compensation, and the accurate generation of its gate bias voltage is quite challenging without using a BGR. The oscillator in [9] which operates at high frequency is able to compensate only process and temperature variations, and also reported that its process variations are over compensated by aiming to achieve better supply compensation. Also, it is expected that there would be a trade off with temperature variations while only achieving process and supply variations which leads to increase in the temperature variations. To achieve accurate frequency compensation for all these PVT variations, the oscillators [7, 8] incorporated a BGR or a regulator. However, these oscillators are able to provide only a moderate compensation of  $\pm 5\%$  for process and temperature variations. In one of the oscillators [8] compensation circuit composed of a constant-gm bias circuit and a regulator consumes no small current of 2.6 mA. Also, the frequency variation of these oscillators [5-8] is expected to increase at higher operating frequencies [10].

To overcome such limitations, we present a PVT-compensated high resolution DCO with a PVT-insensitive digitally controlled current source (DCCS) and a process and temperature (PT)-counteracting voltage regulator. The DCCS provides a digitally controlled current which is insensitive to PVT variations using a PVT-insensitive bias current generator with a BGR. The PT-counteracting regulator provides to the ring oscillator the supply voltage which is varied to counteract to the effect of process and temperature variations while providing supply and load regulation.

The rest of this paper is organized as follows. Section II describes our proposed DCO approach and its implementation in ADPLL. In Section III, we present measurement results from the prototype, and we summarize the paper with conclusions in Section IV.

# II. PROPOSED DIGITALLY CONTROLLED OSCILLATOR

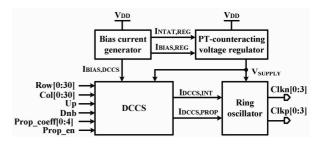

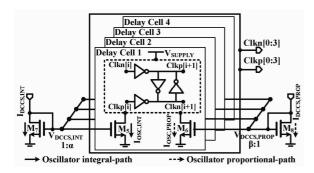

Fig. 1 shows the block diagram of the proposed PVT-compensated DCO, which consists of an eight-phase

Fig. 1. DCO architecture.

Fig. 2. Bias current generator.

current-controlled ring oscillator, a DCCS, a bias current generator, and a PT-counteracting voltage regulator. The DCCS generates PVT-insensitive digitally controlled integral- and proportional-path currents,  $I_{DCCS,INT}$  and  $I_{DCCS,PROP}$ , set by the integral-path frequency control code word (FCW) and the proportional-path FCW, respectively. Its PVT-insensitive reference bias current,  $I_{BIAS,DCCS}$ , is generated by the bias current generator. The PT-counteracting voltage regulator generates a variable supply voltage,  $V_{SUPPLY}$ , in response to PVT variations using the PVT-insensitive bias current,  $I_{BIAS,REG}$ , of the bias current generator and the negative-to-absolute temperature (NTAT) current,  $I_{NTAT,REG}$ , of the BGR. The variable supply voltage,  $V_{SUPPLY}$ , supplies the DCCS and the ring oscillator. The eight-phase current controlled ring oscillator generates equally-spaced multiphase clock signals, Clkn[0:3] and Clkp[0:3], with a frequency controlled by  $I_{DCCS,INT}$  and  $I_{DCCS,PROP}$ . The bias current generator and the regulator are supplied by an external supply voltage,  $V_{DD}$ .

#### 1. Bias Current Generator

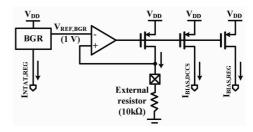

Fig. 2 shows a bias current generator circuit which converts the reference voltage of BGR,  $V_{REF,BGR}$ , into the PVT-insensitive bias currents  $I_{BIAS,DCCS}$  and  $I_{BIAS,REG}$ , which are supplied to the DCCS and the PT-counteracting voltage regulator. It also provides the

Fig. 3. (a) BGR, (b) BGR operational amplifiers.

$I_{NTAT,REG}$  current from its BGR to the regulator. A stable external resistor is used in this bias current generator as a reference. Current mirroring is used to distribute bias currents for various sub-blocks in the chip.

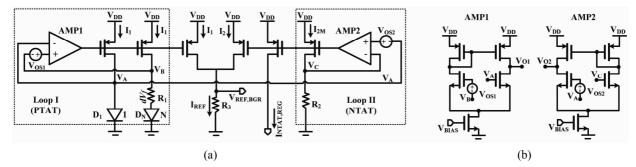

The BGR used in the bias current generator consists of a special current-summing method that reduces the output sensitivity to the operational amplifiers offset voltages of the operational amplifiers as shown in Fig. 3(a). The BGR circuit has two loops: a proportional- toabsolute temperature (PTAT) loop generates a variable current with a positive temperature coefficient (TC), and an NTAT loop which generates a current with a negative TC. In the PTAT loop, the voltage difference between the inputs of diodes  $D_I$  and  $D_N$  is  $d_{Vf}$ , which is proportional to the product of the thermal voltage  $V_T$  and ln(N), where N represents the ratio of the junction areas of the two diodes. The PTAT current  $I_1$  has a positive TC, since the thermal voltage  $V_T$  is proportional to the absolute temperature. In the NTAT loop, the forward bias voltage  $V_{fl}$  of  $D_l$  changes in the opposite direction to the temperature variation, so the current  $I_2$  will have a negative TC. The summing of these two currents by choosing appropriate values for the resistors  $(R_1, R_2, and$  $R_3$ ), we generate a zero TC reference voltage,  $V_{REF,BGR}$ . The operational amplifiers bias voltage,  $V_{BLAS}$ , is generated using a diode-connected PMOS transistor and a resistor. The two operational amplifiers used in the BGR have systematic and random offset voltages, leading to current errors in their outputs. We partially overcome this by taking advantage of the offset-matching characteristic of these operational amplifiers. The errors in the output currents cancel each other if the systematic offsets of these two operational amplifiers are made to oppose each other by connecting the outputs of the differential pairs directly in one operational amplifier,

and making a cross connection in the other, as shown in Fig. 3(b). The output errors due to the matching offsets,  $V_{OSI}$  and  $V_{OS2}$ , will then cancel each other, as expressed by the following expression for  $V_{REF,BGR}$ :

$$V_{REF,BGR} = \left(\frac{R_3}{R_1}\right) \cdot dV_f + \frac{R_3}{M \cdot R_2} \cdot V_{f1}$$

$$-\left(\frac{R_3}{R_1} \cdot V_{OS1} - \frac{R_3}{M \cdot R_2} \cdot V_{OS2}\right) \tag{1}$$

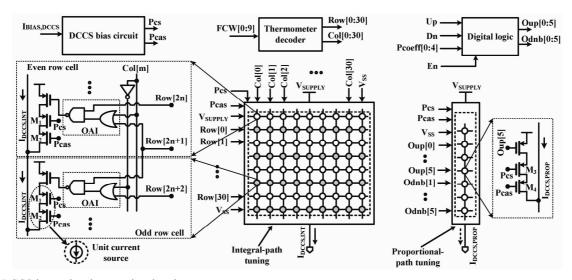

# 2. Digitally Controlled Current Source

The proposed DCCS is implemented with integral- and proportional-path tuning circuits, as shown in Fig. 4. Its integral-path tuning is implemented with 1024 PMOS unit current sources rather than the unit resistors of [3, 4]. All these unit cells are identical and connected in an array, but they are arranged with even- and odd-numbered cells. The 10-bit integral-path FCW is converted into row and column thermometer codes to control the segmented array of current sources. Progression of an example integral-path FCW is discussed in [3] and shows how to avoid glitches with the thermometer code when FCW is incremented or decremented by one. The unit cell current source is composed of two current source PMOS transistors,  $M_1$  and  $M_2$ , and a digital logic implemented with an or-and-invert (OAI) gate. All the transistors of the bias circuit as well as the unit cell transistors,  $M_1$  and  $M_2$ , operate in saturation. All these unit cells generate a PVT-insensitive current over all PVT variations, since they are mirrored by the PVT-insensitive bias current,  $I_{BLAS,DCCS}$ , via Pcs and Pcas. The DCCS produces a PVTinsensitive integral-path current,  $I_{DCCS,INT}$ , with FCW by adding all these unit-cell currents together.

Fig. 4. DCCS integral and proportional tuning.

The DCCS proportional-path tuning is composed of twelve PMOS unit current sources in a linear array and a digital logic, unlike the capacitors at the delay cell output of [4]. Its PMOS unit current source is similar to the design of the DCCS integral tuning PMOS unit cell. The proportional-path tuning circuit is enabled by the En signal and its change in current polarity is determined by the Up and Dn signals. These unit cell currents are added together to generate a DCCS proportional-path tuning current,  $I_{DCCS,PROP}$ . The tuning circuit is used for adaptive proportional gain control of the ADPLL, using 5 bits of the proportional coefficient to reduce the ADPLL jitter [4].

# 3. Ring oscillator

The ring oscillator is composed of four identical differential delay cells, as shown in Fig. 5, each of which consists of two main inverters, two latch inverters, and two NMOS current source transistors ( $M_5$  and  $M_6$ ). The delay cells currents,  $I_{OSC,INT}$  and  $I_{OSC,PROP}$ , are determined by the NMOS current source transistors, which are in turn controlled by mirroring the DCCS integral- and proportional-path tuning currents,  $I_{DCCS,INT}$  and  $I_{DCCS,PROP}$ , to generate eight multiphase clock signals, Clkn[0:3] and Clkp[0:3].

Therefore, the frequency of the ring oscillator varies proportional to its DCCS tuning current. The frequency of an N-stage ring oscillator,  $F_{OSC}$ , is expressed primarily as

$$\begin{split} F_{OSC} &= \frac{I_{OSC,INT} + I_{OSC,PROP}}{2 \cdot N \cdot C_L \cdot V_{SWING}} \\ &= \frac{\alpha \cdot I_{DCCS,INT} + \beta \cdot I_{DCCS,PROP}}{2 \cdot N \cdot C_L \cdot V_{SWING}}, \end{split} \tag{2}$$

where N is the number of delay cells,  $C_L$  is the load capacitance of the delay cell,  $V_{SWING}$  is the rail-to-rail voltage swing of the oscillation,  $\alpha$  and  $\beta$  are the integral and proportional current ratio of the oscillator and the DCCS, respectively.

From (2), we see that the oscillation frequency is primarily determined by the PVT-insensitive DCCS integral- and proportional-path tuning currents and the oscillator voltage swing,  $V_{SWING}$ , which is same as  $V_{SUPPLY}$ . However, the PVT-insensitive DCCS current with a constant  $V_{SUPPLY}$  alone cannot achieve the frequency compensation fully for PVT variations, since various other factors such as variations in transistor threshold voltage, mobility, channel length, width, gate oxide capacitance, and load capacitance due to process and temperature variations can have secondary effects on the oscillation [6-11]. To compensate these secondary variations further, the oscillator supply voltage,  $V_{SUPPLY}$ , must be varied instead of just regulating the output voltage at a constant value.

## 4. PT-counteracting Voltage Regulator

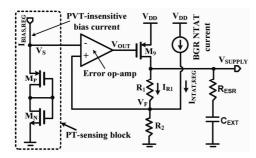

In our voltage regulator, we have adapted a regulator which compensates the oscillator process and

Fig. 5. Ring oscillator.

Fig. 6. PT-counteracting voltage regulator.

temperature variations [8] to generate  $V_{SUPPLY}$  which reflects PT variations to counter-act the effect of the PT variation of the ring oscillator due to secondary effects. As shown in Fig. 6, it consists of a PT-sensing block with diode-connected NMOS and PMOS transistors,  $M_N$  and  $M_P$ , an error op-amp, a PMOS pass transistor  $M_9$ , and feedback resistors  $R_I$  and  $R_2$ .

The PT-counteracting voltage regulator uses the PVT-insensitive bias current,  $I_{BIAS,REG}$ , from the proposed bias current generator instead of using a separate constant- $g_m$  bias circuit current [8]. This approach also helps to overcome the power overhead of constant- $g_m$  bias circuit. The PT-sensing block generates a process and temperature-dependent voltage,  $V_S$ , from  $I_{BIAS,REG}$ , from which the regulator generates a supply voltage which reflects PT changes. Here, the transistors  $M_N$  and  $M_P$  are the replica of ring oscillator delay cell transistors. The sense output  $V_S$  is expressed as

$$V_{S} = V_{TH,N} + \left| V_{TH,P} \right| + \sqrt{\frac{2 \cdot I_{BIAS,REG}}{C_{OX,N} \cdot \mu_{N}} + \frac{2 \cdot I_{BIAS,REG}}{C_{OX,P} \cdot \mu_{P}}}.$$

(3)

The NTAT current,  $I_{NTAT,REG}$ , from the BGR, having a negative temperature coefficient, is used to compensate

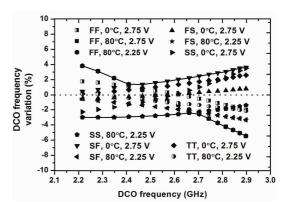

Fig. 7. Simulated overall DCO frequency variations for PVT.

the  $V_{SUPPLY}$  dependency with temperature variations. The feedback node voltage,  $V_F$ , is expressed as

$$V_F = \left(\frac{R_2}{R_1 + R_2}\right) \cdot V_{SUPPLY} + \left(\frac{R_1 \cdot R_2}{R_1 + R_2}\right) \cdot I_{NTAT,REG}. \tag{4}$$

Thus, the output voltage of regulator is expressed as

$$V_{SUPPLY} = \left(1 + \frac{R_1}{R_2}\right) \cdot V_S - R_1 \cdot I_{NTAT, REG.}$$

(5)

From (5), the generated  $V_{SUPPLY}$  is a function of  $V_S$  and  $I_{NTAT,REG}$  and it can be adjusted by properly selecting the resistances  $R_I$  and  $R_2$ .

Under process variations, for example, when the circuit is in FF<sup>1</sup> process corner, the node voltage  $V_S$ decreases, since the mobilities,  $\mu_N$  and  $\mu_P$ , increase and the threshold voltages,  $V_{TH,N}$  and  $|V_{TH,P}|$ , decrease [9]. Hence, from (5), the  $V_{SUPPLY}$  decreases causing the ring oscillator to slow down. Basic assumption is that the voltage across the diode-connected pair flowing the constant current tracks the voltage required to yield a constant delay time. Hence, with SS process corner,  $V_{SUPPLY}$  will increase to speed up the delay time of the cell. However, under skewed process corners such as FS and SF corner, the delay tends to be determined by the sum of variations and therefore its effect is equivalent to TT process corner. Under supply voltage variation,  $V_S$ does not change since the PT-sensing block is supplied by the PVT-insensitive bias current.

<sup>&</sup>lt;sup>1</sup> The process corner 'XY' refers to 'NMOS: X and PMOS: Y', with X and Y replaced by either of F=fast, S=slow, and T=typical.

| PT Corners (V <sub>DD</sub> = 2.5 V) | Required        | Achieved          |                 |                 |                     |  |

|--------------------------------------|-----------------|-------------------|-----------------|-----------------|---------------------|--|

|                                      | $V_{SUPPLY}(V)$ | $V_S(\mathbf{V})$ | $V_{SUPPLY}(V)$ | $F_{OSC}$ (GHz) | Frequency Error (%) |  |

| FF, 0°                               | 0.889           | 0.823             | 0.896           | 2.517           | 0.676               |  |

| FF, 40°                              | 0.896           | 0.782             | 0.898           | 2.504           | 0.144               |  |

| FF, 80°                              | 0.902           | 0.743             | 0.905           | 2.506           | 0.220               |  |

| FS, 0°                               | 1.044           | 0.886             | 1.043           | 2.498           | -0.072              |  |

| FS, 40°                              | 1.060           | 0.845             | 1.044           | 2.478           | -0.868              |  |

| FS, 80°                              | 1.079           | 0.805             | 1.050           | 2.463           | -1.488              |  |

| TT, 0°                               | 1.041           | 0.893             | 1.060           | 2.523           | 0.924               |  |

| TT, 40°                              | 1.061           | 0.852             | 1.062           | 2.500           | 0.000               |  |

| TT, 80°                              | 1.089           | 0.813             | 1.068           | 2.483           | -0.684              |  |

| SF, 0°                               | 1.045           | 0.901             | 1.077           | 2.538           | 1.504               |  |

| SF, 40°                              | 1.066           | 0.860             | 1.080           | 2.516           | 0.628               |  |

| SF, 80°                              | 1.084           | 0.821             | 1.087           | 2.504           | 0.172               |  |

| SS, 0°                               | 1.245           | 0.967             | 1.225           | 2.483           | -0.672              |  |

| SS, 40°                              | 1.285           | 0.926             | 1.226           | 2.456           | -1.760              |  |

| SS, 80°                              | 1.332           | 0.887             | 1.233           | 2,431           | -2.780              |  |

Table 1. DCO required and achieved variable supply voltages

When the temperature increases, the threshold voltages and the mobilities of  $M_P$  and  $M_N$  transistors decrease [11]. Since the decrease in threshold voltages dominate the decrease in mobilities unless the currents flowing through those transistors are much larger than their zero temperature coefficient (ZTC) currents [11],  $V_{SUPPLY}$  decreases along with  $V_S$ . At the same time, the decrease in  $I_{NTAT,REG}$  due to the negative temperature coefficient helps to increase the  $V_{SUPPLY}$ . Hence, combined effect of  $V_{SUPPLY}$  can be made to increase slightly in order for the ring oscillator to speed up with the overall effect of constant oscillation frequency.

The second column in Table 1 shows the simulation results of the required supply voltages for the oscillator to generate an oscillation frequency of 2.5 GHz under process and temperature variations shown in the first column. The numbers in the fourth column indicates the generated  $V_{SUPPLY}$  by the PT-counteracting regulator which would ideally be identical to the numbers in the second column under the same PT conditions.  $R_1$  (190  $k\Omega$ ), R<sub>2</sub> (156  $k\Omega$ ) and I<sub>NTAT,REG</sub> (4.3  $\mu$ A) are selected to give the minimum errors over all process and temperature corners as well as all DCCS FCWs. In our design,  $V_{SUPPLY}$  is also used as DCCS supply voltage to track PVT variations more closely. The simulation results of our overall DCO frequency variations from its typical PVT corner (TT, 40°C, 2.5 V) across all FCWs with the frequency range of 2.2 GHz to 2.9 GHz are shown in Fig. 7. The DCO frequency variation is 3.8% to -3.0% at 2.2

GHz, 1.5% to -2.8% at 2.5GHz, and 3.6% to -5.5% at 2.9 GHz.

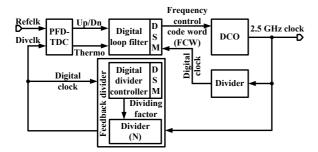

#### 5. DCO Implementation in ADPLL

The block diagram of an ADPLL is shown in Fig. 8 which consists of a phase-frequency-detecting time-todigital converter (PFD-TDC) [12], a second-order synthesizable digital loop filter (DLF), an 8-bit firstorder delta-sigma modulator (DSM) for DCO, a DCO, a divider for the DLF, and a feedback divider. The ADPLL uses a reference clock, Refclk, of 40-MHz frequency. The PFD-TDC compares the arrival time of the Refclk edge with that of divided DCO clock, Divclk, edge, and generates Up, Dn signals, and also a thermometer code, Thermo. The DLF is used to filter the phase noise, and the resulting values are fed into the DSM to dither the output clock of the DCO with its generated FCW to improve the frequency resolution. The output frequency of the DCO is divided by a feedback divider having a dividing factor of N to generate Divclk. A second-order DSM is used to randomize the dividing factor of the feedback divider through its digital divider controller.

### III. MEASUREMENT RESULTS

The proposed DCO is implemented in a fractional-*N* ADPLL to verify its applicability to enhance the ADPLL performance. The ADPLL with the proposed DCO has

Fig. 8. Fractional-N ADPLL block diagram.

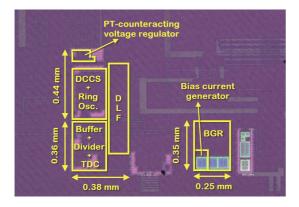

Fig. 9. ADPLL die microphotograph.

been fabricated using 65 nm CMOS technology and its die photomicrograph is shown in Fig. 9. Excluding BGR, the DCO occupies 0.074 mm<sup>2</sup>. The area consumed by the BGR is excluded since it is a common block shared with other blocks.

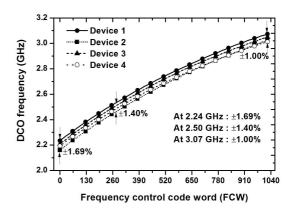

Fig. 10 is a plot of measured DCO frequency gain curve for four sample devices at room temperature with 2.5 V supply voltage. The frequency variation at the minimum frequency of 2.24 GHz is  $\pm 1.69\%$  and that at the maximum frequency of 3.07 GHz is  $\pm 1.00\%$ . At 2.5 GHz, the measured frequency variation at room temperature is  $\pm 1.4\%$  which is in good agreement with the simulated process variation of +0.58% to -1.70%. Therefore, the accurate PVT-insensitive current of DCCS and the additional process compensation by the PTcounteracting voltage regulator achieve good frequency compensation across all process variations. The DCO operates with the tuning range of 0.83 GHz and with an average resolution of 0.81 MHz. The resolution varies between 0.59 MHz and 1.08 MHz because, although the DCCS tuning current is linear with the control code, the DCO frequency is nonlinear. For better linearity, the size of the DCCS unit cells can be varied [4].

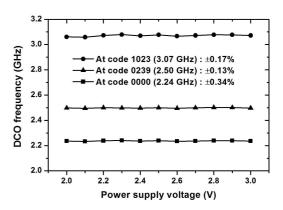

The measured DCO frequency variations at room

Fig. 10. Measured tuning frequency with FCW.

Fig. 11. Measured DCO frequency against supply variation.

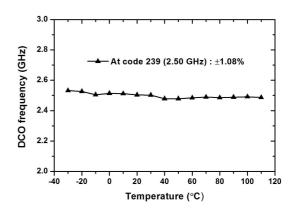

Fig. 12. Measured DCO frequency against temperature.

temperature for Device 1 against the supply voltage variation are shown in Fig. 11. For the supply voltage variation from 2.0 V to 3.0 V, the measured frequency varies by  $\pm 0.13\%$  at 2.5 GHz which is quite small as the PT-counteracting voltage regulator provides a constant supply voltage across supply variations to both the DCCS, which is itself supply insensitive, and the ring oscillator. Fig. 12 shows that the measured DCO

|                                 |             | [5]                     | [6]                         | [7]                      | [8]                            | This work                                    |

|---------------------------------|-------------|-------------------------|-----------------------------|--------------------------|--------------------------------|----------------------------------------------|

| Technology                      |             | CMOS 0.18 μm            | CMOS 90 nm                  | CMOS 0.18 μm             | CMOS 0.13 μm                   | CMOS 65 nm                                   |

| Supply Voltage                  |             | 1.8 V                   | 1 V                         | 1.8 V                    | 3.3 V                          | 2.5V                                         |

| Number of Phases                |             | 6                       | 3                           | 6                        | 4                              | 8                                            |

| Center Frequency                |             | 130 MHz                 | 1.8 GHz                     | 632 MHz                  | 1.25 GHz                       | 2.5 GHz                                      |

| Tuning F                        | Range       | N/A                     | N/A                         | N/A                      | 380 MHz                        | 830 MHz                                      |

| Phase Noise<br>at 10 MHz offset |             | N/A                     | -103.87 dBc/Hz<br>at 2 GHz. | -92 dBc/Hz<br>at 632 MHz | -108dBc/Hz<br>at 1.25 GHz      | -112 dBc/Hz<br>at 2.8 GHz                    |

| Frequency<br>Variation          | Process     | ±1.13%                  | 5.80% (167 chips)           | 4.40% (6 chips)          | ±5%                            | ±1.40% (4 chips)                             |

|                                 | Temperature | ±4.99% (0°C~100°C)      | 0.47%<br>(6.8°C~61.8°C)     | 5.60%<br>(0°C~80°C)      | (15 chips and -<br>40°C~125°C) | ±1.08%<br>(-30°C~110°C)                      |

| for PVT                         | Voltage     | ±5.40%<br>(1.62V~0.12V) | N/A                         | N/A                      | N/A                            | ±0.13% (2.0V~3.0V)                           |

| BGR and Regulator               |             | NO                      | NO                          | YES                      | YES                            | YES                                          |

| Current Consumption             |             | 1.52 mA<br>@ 130 MHz    | 0.087 mA<br>@ 1.8 GHz       | 0.74 mA<br>@ 632 MHz     | 3.4 mA<br>@ 1.25 GHz           | 2.3 mA<br>@ 2.24 GHz<br>3.1 mA<br>@ 3.07 GHz |

Table 2. Performance comparison of the DCO

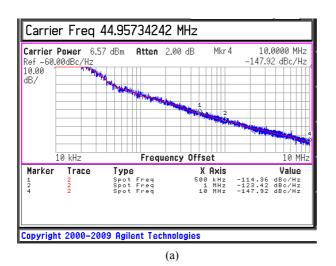

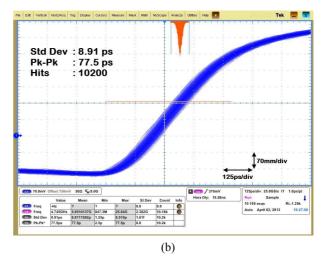

Fig. 13. ADPLL (a) DCO phase noise, (b) Jitter performance.

frequency varies by ±1.08% at 2.5 GHz for temperatures from -30°C to 110°C. The measured DCO frequency variation for temperatures from -30°C to 110°C is in good agreement with the simulation result of +1.71% to -0.92% at the TT process corner. Therefore, the DCCS PVT-insensitive current achieves better temperature compensation. Moreover, its small frequency undercompensation is compensated by the slight increase in the supply voltage of the PT-counteracting voltage regulator as the temperature increases. The temperature variations of the DCO frequency were measured at intervals of 10°C, using a temperature chamber. As shown in Fig. 13(a), the DCO has a phase noise of -112 dBc/Hz at 10 MHz frequency offset with the operating frequency of 2.8 GHz. The DCO frequency and the phase

noise were measured at the divider output due to limited number of package pins, having a dividing factor of 62.5. At its locking condition, the ADPLL with the bandwidth of 1.3 MHz exhibits an RMS jitter of 8.9 ps and a peak-to-peak jitter of 77.5 ps as shown in Fig. 13(b).

The DCO consumes a current varying from 2.3mA at 2.24 GHz to 3.1 mA at 3.07 GHz. The buffer used in this oscillator consumes 1.2 mA to drive the ADPLL blocks with a 50% duty cycle. The bias current generator including BGR and the regulator circuits consume less than 280  $\mu A$  and 28  $\mu A$ , respectively, across all PVT corners. Table 2 compares this DCO with other PVT compensation oscillator designs [5-8]. It is observed that the proposed DCO has lower phase noise than the other PT or PVT-compensated oscillators, and also it has a

wide tuning range whereas the others have no tuning range [5-7] or only a moderate tuning range [9]. Also, it operates at a high operating frequency while generating eight multiphase clock signals. The current consumption of this DCO is relatively higher than the other oscillators except [8] due to its high frequency of operation and a wide tuning range. Overall, the proposed DCO achieved the lowest frequency variation of  $\pm 2.6\%$  at 2.5 GHz for a wide range of PVT variations among the oscillators which are able to achieve only a moderate frequency compensation across either PVT or only PT variations.

#### V. CONCLUSIONS

We present a 2.5 GHz digitally controlled oscillator with a PVT-insensitive DCCS, PT-counteracting voltage regulator and bias current generator for offering a PVTinvariant and predictable oscillation frequency with low variations. It reduces the frequency variations down to  $\pm 2.6\%$  at 2.5 GHz across all PVT corners. The oscillator control current is generated by the DCCS PVTinsensitive tuning current using bias current generator with BGR to compensate PVT variations and its variable supply voltage is generated by the PT-counteracting voltage regulator to counter act the process and temperature variations further. The ADPLL with the proposed DCO has been fabricated using a CMOS 65nm technology. The 10-bit DCO has a wide tuning range of 2.24 GHz to 3.07 GHz with a high resolution of 0.81 MHz and with an 8-bit DSM of 3.1 kHz, while consuming between 2.3 mA and 3.1 mA. It exhibits a phase noise performance of -112 dBc/Hz at a 10 MHz offset, and the ADPLL has an RMS jitter of 8.9 ps.

# ACKNOWLEDGMENTS

The authors would like to thank IC Design Education Center (IDEC) for the provision of CAD tools, and the Inter-University Semiconductor Research Center (ISRC) for the measurement equipment.

#### REFERENCES

[1] T. Olsson and P. Nilsson, "A digitally controlled PLL for SoC Applications," *IEEE J. Solid-State Circuits*, vol. 39, no. 5, pp. 451–460, May 2004.

- [2] D.-S. Kim, H. Song, T. Kim, S. Kim, and D.-K. Jeong, "A 0.3-1.4 GHz all-digital fractional-N PLL with adaptive loop gain controller," *IEEE J. Solid-State Circuits*, vol. 45, no. 11, pp. 2300–2311, Nov. 2010.

- [3] D.-H. Oh, D.-S. Kim, S. Kim, D.-K. Jeong, and W. Kim, "A 2.8Gb/s all-digital CDR with a 10b monotonic DCO," in Proc. *IEEE Int. Solid-State Circuits Conf.*, pp.222-598, 2007.

- [4] H. Song, D.-S. Kim, D.-H. Oh, S. Kim, and D.-K. Jeong, "A 1.0–4.0-Gb/s all-digital CDR with 1.0-ps period resolution DCO and adaptive proportional gain control," *IEEE J. Solid-State Circuits*, vol. 46, no. 2, pp. 424–434, Feb. 2011.

- [5] C.-F. Tsai, W.-J. Li, P.-Y. Chen, Y.-Z. Lin, and S.-J. Chang, "On-chip reference oscillators with process, supply voltage and temperature compensation," in Proc. Int. Symp. Next-Generation Electronics, pp. 108-111, 2010, Taiwan.

- [6] X. Zhang and A. B. Apsel, "A low-power, processand-temperature -compensated ring oscillator with addition-based current source," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, pp. 868–878, 2011.

- [7] R. Vijayaraghavan, S. K. Islam, M. R. Haider, and L. Zuo, "Wideband injection-locked frequency divider based on a process and temperature compensated ring oscillator," *IET Circuits, Devices* & Syst., vol. 3, pp. 259–267, 2009.

- [8] K. R. Lakshmikumar, V. Mukundagiri, and S. L. J. Gierkink, "A process and temperature compensated two-stage ring oscillator," in Proc. IEEE Custom Integr. Circuits Conf., pp. 691–694, 2007.

- [9] Y.-S. Park and W.-Y. Choi, "On-chip compensation of ring VCO oscillation frequency changes due to supply noise and process variation," *IEEE Trans. Circuits Sys.-II, Exp. Briefs*, vol. 59, no. 2, pp. 73–77, Feb. 2012.

- [10] M. Nekili, Y. Savaria, and G. Bois, "Spatial characterization of process variations via MOS transistor time constants in VLSI and WSI," *IEEE J. Solid-State Circuits*, vol. 34, no. 1, pp. 80–84, Jan. 1999.

- [11] I. M. Filanovsky and A. Allam, "Mutual compensation of mobility and threshold voltage temperature effects with applications in CMOS circuits," *IEEE Trans. on Circuits Syst. I*,

*Fundamental Theory and Applications*, vol. 48, no. 7, pp. 876–884, July 2001.

[12] D.-H. Oh, K.-J. Choo, and D.-K. Jeong, "Phase-frequency detecting time-to-digital converter," *IET Electronics Letters*, vol. 45, no: 4, pp.201-202, Dec. 2009.

Anil Kavala was born in India in 1985. He received the B.Tech. degree in electronics and communication engineering from Jawaharlal Nehru Technological University, India, in 2006, and the M.S. degree in electrical engineering from Korea

Advanced Institute of Science and Technology, Daejeon, Korea in 2009. Currently, he is pursuing his Ph.D. degree in Electrical engineering at Seoul National University. His research interests include analog and mixed-signal integrated circuit design.

Woorham Bae received the B.S. degree in electrical engineering from Seoul National University, Seoul, Korea, in 2010. He is currently working towards the Ph.D degree at the same university. His research is

focused on high-speed I/O circuits and architectures.

**Sungwoo Kim** was born in Daegu, Korea in 1986. He received the B.S. degree in electrical engineering from Kyungpook National University, Daegu, Korea in 2009, and the M.S. degree in electrical engineering from

Seoul National University, Seoul, Korea in 2011. He is currently working towards the Ph.D degree at the same university. His research is focused on high-speed I/O circuits and architectures.

**Gi-Moon Hong** received the B.S. and M.S. degrees in electrical engineering from Seoul National University, Seoul, Korea, in 2009 and 2011, respectively. Since 2011, he is working towards the Ph.D. degree at

the same university. His research interests include low-power and high-speed serial link circuits and memory interface.

Han-Kyu Chi was born in Inchon, Korea, in 1982. He received the B.S., M.S., and Ph.D degree in electronics engineering from Seoul National University, Seoul, Korea, in 2005, 2007, and 2013, respectively. In 2014, he joined at SK Hynix, Korea where

he has been working in the area of high-speed interface circuit design. His research interests include clock and data recovery for high-speed communication and silicon photonics.

**Suhwan Kim** received the B.S. and M.S. degrees in electrical engineering and computer science from Korea University, Seoul, Korea, in 1990 and 1992, respectively, and the Ph.D. degree in electrical engineering and computer science from the University

of Michigan, Ann Arbor, in 2001. From 1993 to 1999, he was with LG Electronics, Seoul. From 2001 to 2004, he was a research staff member at the IBM T. J. Watson Research Center, Yorktown Heights, NY. In 2004, he joined Seoul National University, Seoul, where he is currently an Associate Professor of electrical engineering. His research interests encompass high-performance and low-power analog and mixed-signal integrated circuits, high-speed I/O circuits, and power electronics. Dr. Kim served as a Guest Editor for IEEE JOURNAL OF SOLID-STATE CIRCUITS special issue on IEEE Asian Solid-State Circuits Conference. He has also served as the General Co-Chair and Technical Program Chair for the IEEE International SOC Conference. He has participated on the Technical Program Committee of the IEEE International SOC Conference, the International Symposium on Low-Power Electronics and Design, the IEEE Asian Solid-State Circuits Conference, and the IEEE International Solid-State Circuits Conference.

**Deog-Kyoon Jeong** received the B.S. and M.S. degrees in electronics engineering from Seoul National University, Seoul, Korea, in 1981 and 1984, respectively, and the Ph.D. degree in electrical engineering and computer sciences from the

University of California, Berkeley, in 1989. From 1989 to 1991, he was with Texas Instruments, Dallas, TX, where he was a Member of Technical Staff and worked on the modeling and design of BiCMOS gates and the single-chip implementation of the SPARC architecture. He joined the faculty of the Department of Electronics Engineering and Inter-University Semiconductor Research Center, Seoul National University, as an Assistant Professor in 1991. He is currently a Professor in the School of Electrical Engineering, Seoul National University. His main research interests include highspeed I/O circuits, VLSI systems design, microprocessor architectures, and memory systems.